Digital Simulation and Verification

A HDL simulation environment that enables you to verify the functional and timing models of your design. Thus, your Design teams can focus on improving existing methodologies with tools that scale across multiple levels of abstraction and design complexity.

- VPI functionality.

- A graphical waveform viewer.

- Supports both VHDL and Verilog designs.

- A Verilog simulator and synthesis tool for IEEE 1364-2001 standard.

- Export signals to a VCD file or a GHW file for visual inspection with a waveform viewer.

- Pretty printing or cross references generation in HTML.

- Makefile generation for any component in a design.

- Achievements: Successfully compiled and run a DLX processor and a LEON1 SPARC processor.

- Automatic layout generation from VHDL description via desired standard cell libraries.

- Implementation of the VHDL language in accordance to the IEEE 1076-1987 standard, IEEE 1076-1993 standard, the protected types of VHDL00 (aka IEEE 1076a or IEEE 1076-2000) and and non-standard third party libraries.

Tools:

GHDL A VHDL simulator, using the GCC technology. GHDL implements the VHDL language according to the IEEE 1076-1987 or the IEEE 1076-1993 standard. It compiles VHDL files and creates a binary that simulates your design.

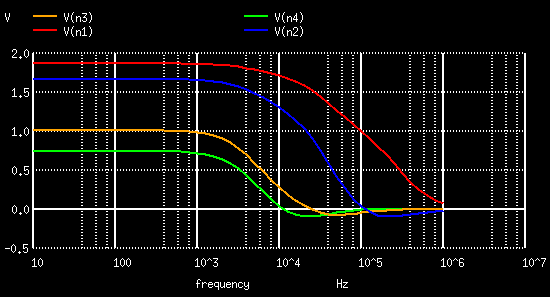

Qucs - A circuit simulator with graphical user interface. The software aims to support all kinds of circuit simulation types, e.g. DC, AC, S-parameter and harmonic balance analysis.

FreeHDL - Yet another VHDL simulator.

Icarus Verilog A Verilog compiler that generates a variety of engineering formats, including simulation. It strives to be true to the IEEE-1364 standard.

More than a simulator.

GTKWave Waveform viewer that can view VCD files produced by most VHDL/Verilog simulation tools, as well as LXT files produced by certain Verilog simulation tools.

Drawtiming - A command line tool for generating timing diagrams from ASCII input files. The input files use a structured language to represent signal state transitions and interdependencies.

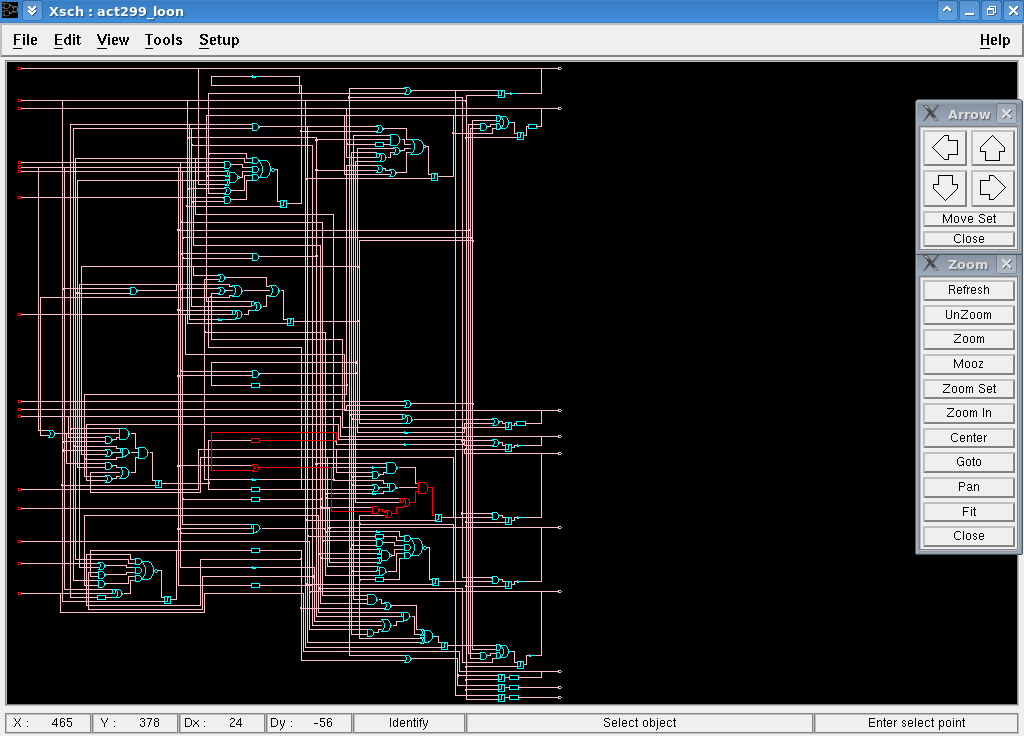

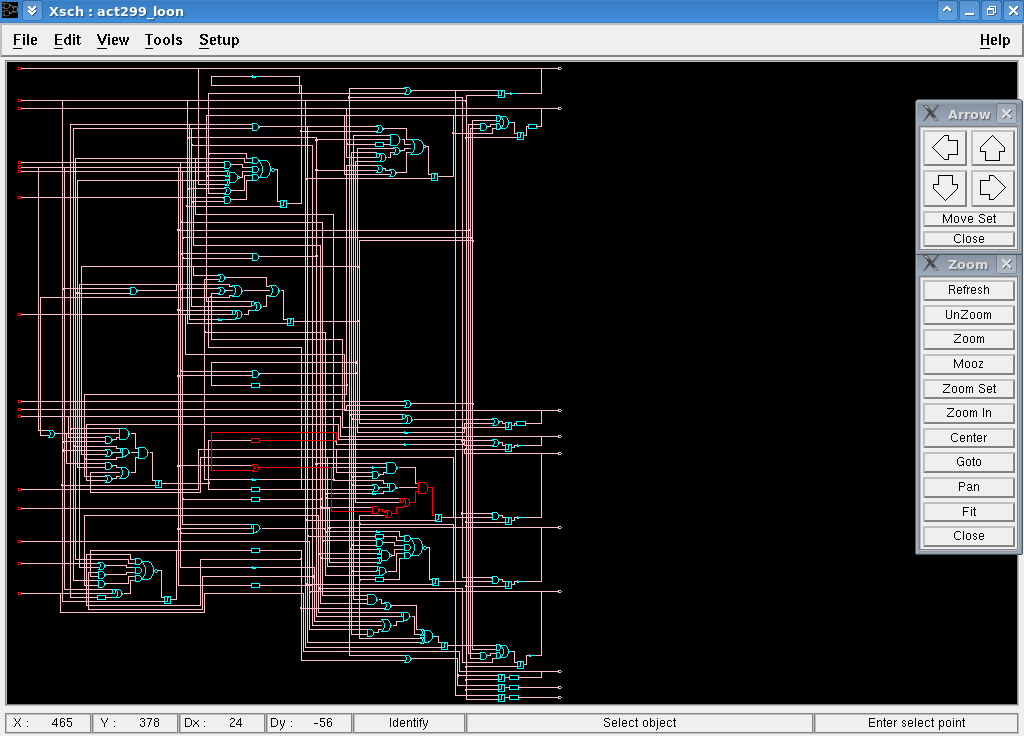

RTL and logic synthesis design flows

- Automatic schematic generation

- VHDL compilation and simulation

- Finite State Machines (FSM)

- Model checking and formal proof

- RTL and Logic synthesis

- Data-Path compilation

- Macro-cells generation

- Symbolic Pad cells

- Design rules checking

- Place and route

- Layout edition

- Netlist extraction and verification

- Automatic Layout generation

- Physical optimization and layout design flows

- Complete RTL to CIF and GDSII flows

- 7 extra standard cells up to a feature size of 0.13µm

- Read/write standard ins/outs including Verilog and VHDL

- Creates a POV-Ray (3D view) scene description file of the GDSII data.

Tools:

pharosc

Tools:

pharosc VLSI and ASIC Technology Standard Cell Libraries

Alliance - a complete set of CAD tools and portable libraries for VLSI design. It includes a VHDL compiler and simulator, logic synthesis tools, and automatic place and route tools.

gds2pov - Creates attractive 3D pictures of a layout. Converts GDS2 layout file to POV-Ray

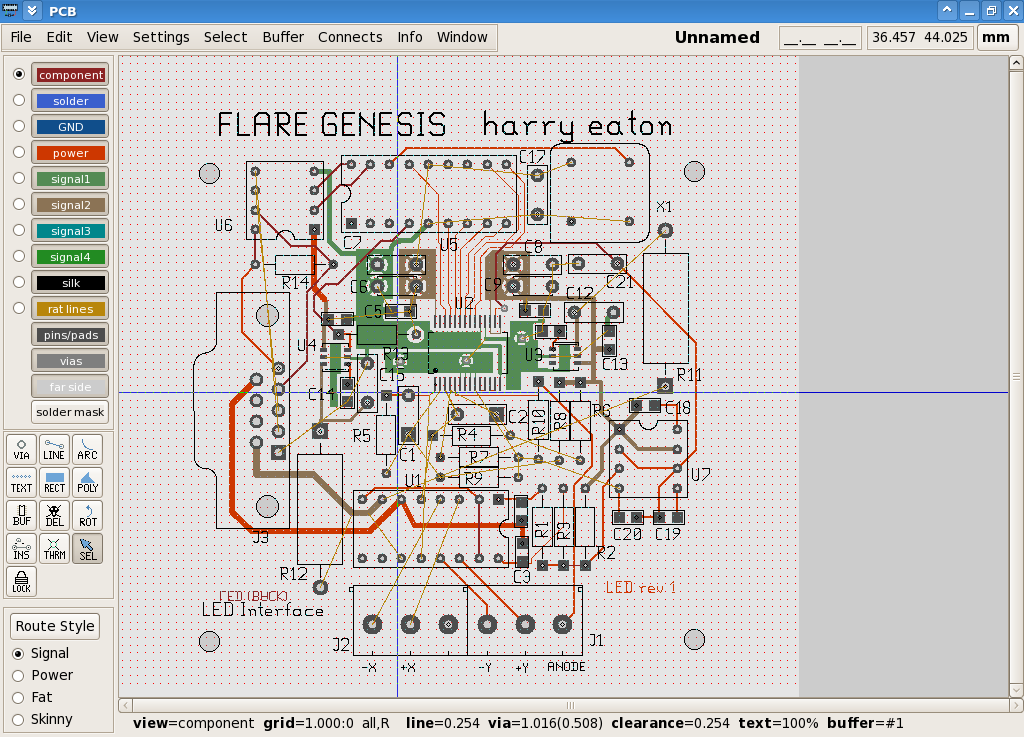

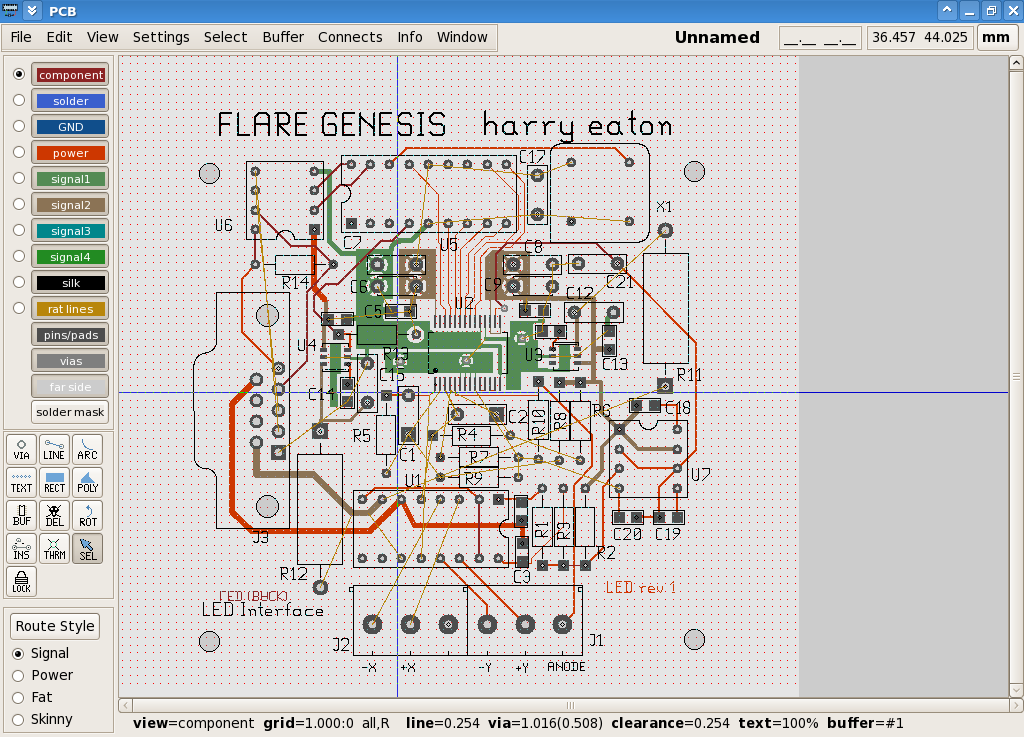

Circuit and PCB Layout

A professional-quality printed circuit board design environment along with :

- schematic capture, simulation, prototyping attribute management,

- bill of materials (BOM) generation and netlisting into over 20 netlist formats.

- Includes a rats nest feature, design rule checking, and can provide industry standard RS-274-X (Gerber), NC drill, and centroid data (X-Y data) output for use in the board fabrication and assembly process.

- Offers high end features such as an autorouter and trace optimizer, which can tremendously reduce layout time.

- Creates PCB of up to 8 layers with an unlimited number of components and nets.

- Includes a viewer for Gerber files (RS274X), which supports NC-drill and Excellon formats.

Tools:

PCB

Tools:

PCB - An interactive printed circuit board editor.

Gerbv - Gerber Viewer (gerbv) is a viewer for Gerber files. Gerber files are generated from PCB CAD system and sent to PCB manufacturers as basis for the manufacturing process.

gEDA/gaf - A full suite of Electronic Design Automation tools.

Kicad - Kicad creates electronic schematic diagrams and printed circuit board artwork up to 16 layers.

CAD Tools

The CAD department of many semiconductor design centers maintain various scripts under various version control systems. We strives to give those CAD engineers some perl modules and a proper platform.

- Revision Control : CVS, SVN, GIT, RCS

- Web based tools : Trac, Bugzilla

- UML to maintain their personalized perl scripts.

Perl Modules:

- VHDL : perl-Hardware-Vhdl-Parser, perl-Hardware-Vhdl-Tidy, perl-Hardware-Vhdl-Lexer

- Verilog : perl-Verilog perl-Verilog-CodeGen perl-Hardware-Verilog-Parser perl-Verilog-Readmem

- Systemc : perl-SystemPerl perl-SystemC-Vregs (Read more about SystemC on Fedora here)

- Generation of documentation : doxygen with VHDL support

- SystemVerilog : perl-Verilog

- Modelsim List: perl-ModelSim-List

µController Programming

Supported compilers :

- the Small Device C Compiler, the GNU PIC Utilities, the PICC compilers,

- the PIC30 toolchain, the C18 compiler, the JAL and JALV2 compilers,

- the CSC compiler, and the Boost compilers.

Ease to use IDEs for microcontrollers circuit design, simulation and programmation to serial, parallel and USB ports.

IDE includes an oscilloscope and a flowchart integration.

Supported debuggers : ICD2 and GPSim.

Supported programmers : ICD2, PICkit1 and PICkit2 and PicStart+ programmers.

Supports 8051 and AVR.

Embedded Systems Development

AVR Development System

Supports the Atmel's STK500 and the PPI (parallel port interface) programmer types.

Includes

- Cross compilers and Programmers

- A Universal In-System Programmer for Atmel AVR and 8051

- A Program for interfacing the Atmel JTAG ICE to GDB

Small Device C Compiler

Special contributions from Fedora Embedded SIG

Project Management and budget tracking

- Gantt Diagram : planner

- Mind mapping tools (excellent for FPGA design) : Vym

- Budget Tracking : Kmymoney, Openoffice Spreadsheet

- System design : Dia, Inkscape

This simulation lab enables design engineers to edit and simulate their schematics.

This simulation lab enables design engineers to edit and simulate their schematics.